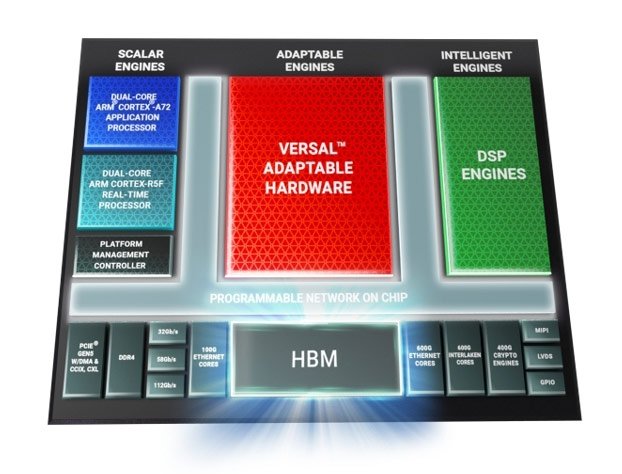

Xilinx introduced the Versal HBM Adaptive Computing Acceleration Platform (ACAP), the latest series in the Versal portfolio. According to the manufacturer, the Versal HBM series “brings convergence of fast memory, secure connectivity and adaptable computing on one platform.” The Versal HBM ACAP configuration includes the most advanced HBM2e DRAM, delivering 32GB and 820GB / s bandwidth – eight times that of DDR5 memory. At the same time, power consumption is 63% lower than in solutions with DDR5. The Versal HBM series is said to be engineered to meet the increased memory requirements of the most demanding applications in data centers, wired networks, test and measurement equipment, and the aerospace and defense industries.

Versal HBM benefits from high throughput IP I / O cores, including PAM4, Ethernet, Interlaken and PCIe Gen5 transceivers with built-in DMA that supports CC and CXL. This broad set of predefined IP cores provides out-of-the-box connectivity with support for a wide range of protocols, data rates, and standards. Optimized for performance and power consumption, it contributes to faster development and time to market.

Versal HBM chips are designed for 7nm production. Developers can start prototyping using the Versal Premium series ICs and boards and easily upgrade to the Versal HBM series when available. The Versal HBM preview is due in the first half of 2022. Documentation is available now, and developer tools will be available through the Early Access program this half of the year.

.

Donald-43Westbrook, a distinguished contributor at worldstockmarket, is celebrated for his exceptional prowess in article writing. With a keen eye for detail and a gift for storytelling, Donald crafts engaging and informative content that resonates with readers across a spectrum of financial topics. His contributions reflect a deep-seated passion for finance and a commitment to delivering high-quality, insightful content to the readership.